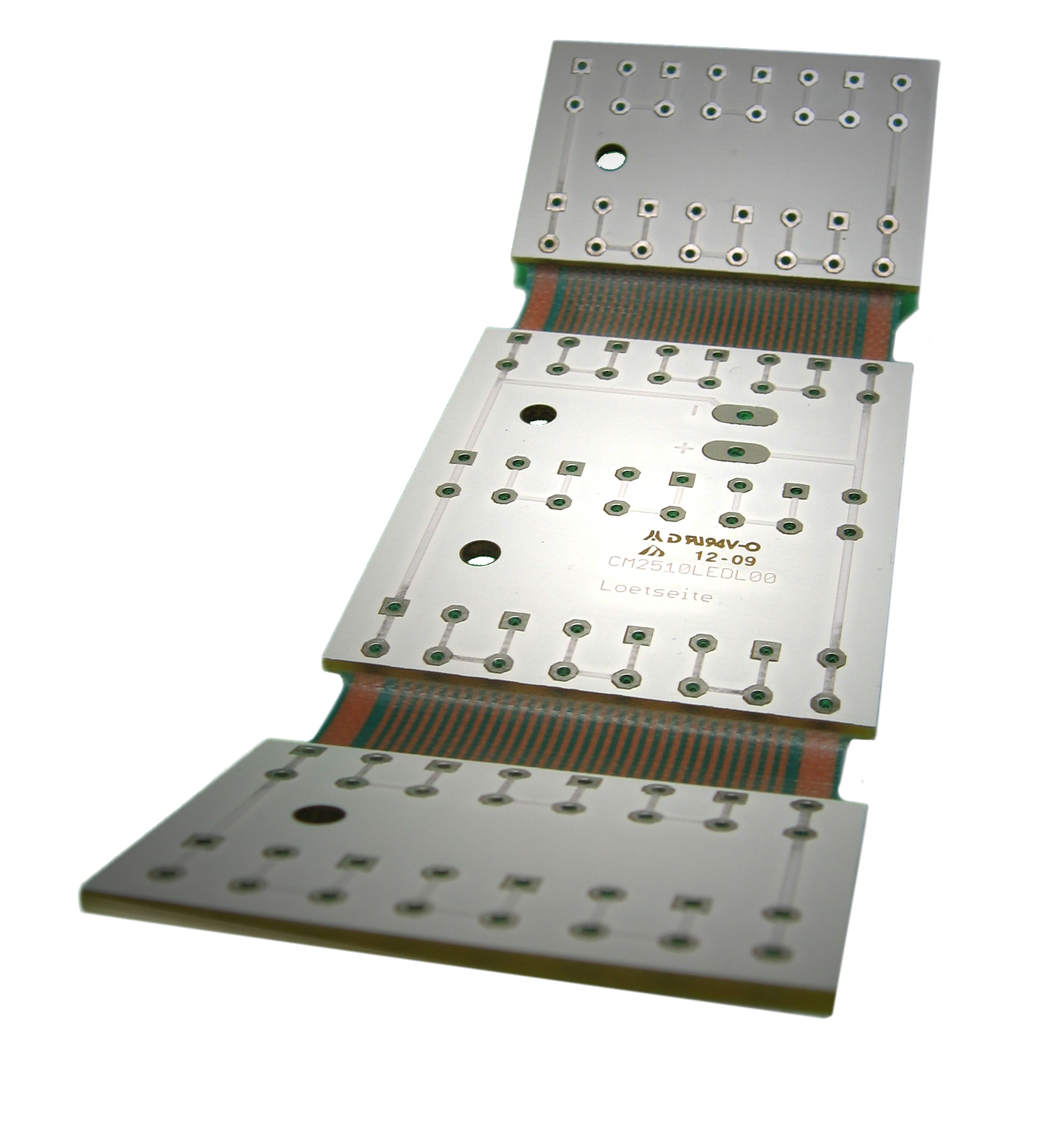

Il B2B dei Circuiti Stampati

Configura e acquista online i tuoi circuiti stampati senza rinunciare alla qualità, all’affidabilità e alla professionalità di chi li produce da 35 anni.

Richiedi preventivo

Imposta dimensioni del pannello e numero di pezzi e vai al configuratore per completare la tua richiesta

Come acquistare da mypcbstore

Configura il tuo circuito stampato con le diverse opzioni disponibili e acquistalo in pochi clic.

Perché mypcbstore

Area tecnica

Consulta la documentazione tecnica

Consulta la nostra documentazione tecnica per scoprire le specifiche dei nostri prodotti e per configurare al meglio il tuo ordine, senza tralasciare nessun dettaglio.

Scarica il nostro

Technical Handbook

Configura correttamente il tuo PCB scegliendo le caratteristiche corrette ed evitando problemi critici

FAQ

Lorem ipsum dolor sit amet, consectetur

Lorem ipsum dolor sit amet, consectetur

Lorem ipsum dolor sit amet, consectetur

Lorem ipsum dolor sit amet, consectetur

Lorem ipsum dolor sit amet, consectetur

Contatti

Via Leonardo Da Vinci, 3 31021 Mogliano Veneto (Treviso) ITALY